TSMC's new COUPE tech ready in 2026

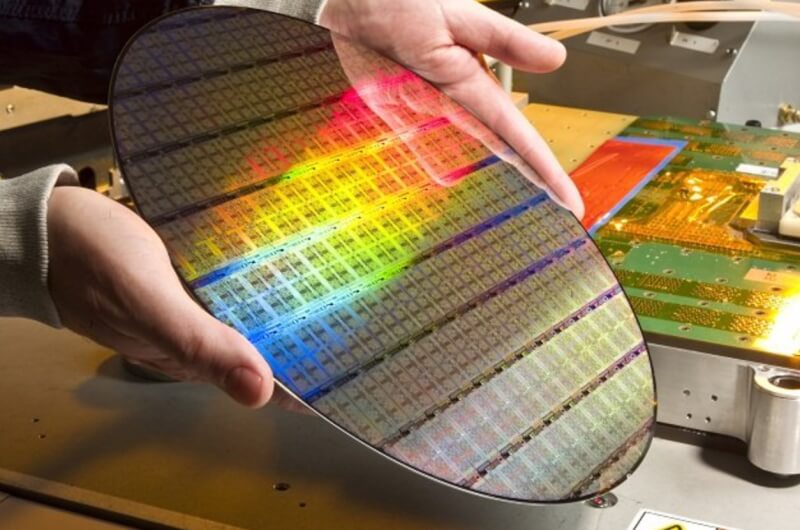

Taiwan Semiconductor Manufacturing Company (TSMC) has unveiled its latest semiconductor process, advanced packaging and 3D IC technologies for next-generation AI innovations at TSMC's Technology Symposium in North America in 2024. At the event, TSMC unveiled its new A16 technology, which features industry-leading nanosheet -transistors with an innovative backside power supply solution for production in 2026, with “significantly improved logic density and performance.

TSMC also introduced its new System-on-Wafer (TSMC-SoW) technology, an innovative solution that delivers "revolutionary wafer-level performance" for future AI requirements for hyperscale data centers. The next-generation COUPE technology uses SoIC-X chip-stacking technology to stack an electrical chip on top of a photonic chip, which TSMC says will offer the lowest impedance at the chip-to-chip interface and higher energy efficiency than conventional methods.

TSMC plans to qualify COUPE for small form factor pluggables in 2025, which will be followed by integration into CoWoS packaging as co-packaged optics (CPO) in 2026, bringing optical connections directly into the chip package. TSMC has also hinted that it is working on a new technology that will power chips from the back of the chip itself, which will speed up AI chips and other processors in 2026 and beyond. TSMC explained in their press release: “TSMC is developing Compact Universal Photonic Engine (COUPE™) technology to support the explosive growth in data transmission that comes with the demand for AI technology.

COUPE uses SoIC-X chip-stacking technology to stack an electrical chip on top of a photonic chip, offering the lowest impedance at the chip-to-chip interface and higher energy efficiency than conventional methods. TSMC plans to qualify COUPE for small form factor pluggables in 2025, followed by integration into CoWoS packaging as co-packaged optics (CPO) in 2026, bringing optical connections directly into the package.

Latest processor - cpu

-

31 Octprocessor - cpu

-

16 Sepprocessor - cpu

AMD Ryzen AI 7 PRO 360 spotted

-

04 Sepprocessor - cpu

Intel scores big AI chip customer

-

04 Sepprocessor - cpu

Exclusively-Intel manufacturing store drawers

-

29 Augprocessor - cpu

Big performance boost for Ryzen CPUs

-

28 Augprocessor - cpu

Intel shares could fall in battle with TSMC and NV

-

28 Augprocessor - cpu

AMD is claimed to have been hacked

-

27 Augprocessor - cpu

Intel presents Lunar Lake, Xeon 6, Guadi 3 chips

Most read processor - cpu

Latest processor - cpu

-

31 Octprocessor - cpu

AMD will launch the Ryzen 7 9800X3D on November 7

-

16 Sepprocessor - cpu

AMD Ryzen AI 7 PRO 360 spotted

-

04 Sepprocessor - cpu

Intel scores big AI chip customer

-

04 Sepprocessor - cpu

Exclusively-Intel manufacturing store drawers

-

29 Augprocessor - cpu

Big performance boost for Ryzen CPUs

-

28 Augprocessor - cpu

Intel shares could fall in battle with TSMC and NV

-

28 Augprocessor - cpu

AMD is claimed to have been hacked

-

27 Augprocessor - cpu

Intel presents Lunar Lake, Xeon 6, Guadi 3 chips